きのうの、

結局、自分の耳障りのいい顧客の声しか聞かないから、顧客第一主義をとっても、事業は傾く

http://blog.goo.ne.jp/xmldtp/e/b248169c7f4afc4506343dbf83557c18

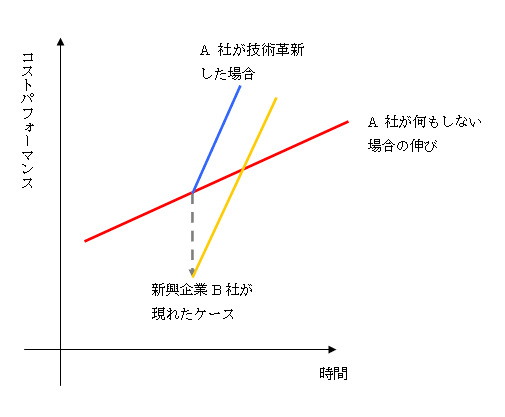

だけど、問題は、既存企業は、新興企業に負けて、撤退にまで追いやられるということ。

つまり、市場がなくなってしまうのだ。

アジャイルとウォーターフォールの関係もそうといえる。

昨日も掲示した、以下の図において

![]()

ウォーターフォールはA社、アジャイルはB社といえる。

アジャイルは、Web開発の場合は有効だけど、

・組み込みの場合、ハードは容易に変更できない

・大規模な場合、ドキュメントが必要になるが、要求仕様や論理的な設計の場合、

デモする術が無いので、イテレーション内に確認して、顧客と同意を取りながら、

開発することができない

(レビューはできるかもしれないが、それが可視化している、進捗わかるとはいえない)

等などの理由により、組み込み、大規模開発には、向かないとされている。

また、ウォーターフォールを採用しているSIerさんは、そういう顧客の意見を聞いているので、

市場の変化に気づかない。

しかし、上記2つは、大きく変わる可能性がある。

■ハードもアジャイル化できる可能性が出てきた

FPGAのエミュレーター(シミュレーターではない)Veloceにより、ハードを製作しなくても(する前に)ソフトウェア開発、テストができるようになった。

また、ハードのテストも、Questa inFactなどにより、制約つきランダムテストよりも高い網羅性と高速のテストが可能になった(人手よりも、当然早い)。

これらにより、ハード設計とソフト開発が同時並行的に進められ、修正スピードも劇的に(100倍以上とか)早くなった。

そうなってくると、・・・ハードもアジャイル?

■要求仕様や論理的な設計のデモも・・・実はできる!

だれもいわないけど、要求仕様や論理的な設計のデモって、実は、できる。

その前に、ライブラリのデモであれば、FDDを採用して、JUnitでテスト環境を作成しておき、

イテレーション内でプログラムを作成、JUnitで通ることを示せば、デモ?できる。

これとおなじレベルであれば、要求仕様のチェックはできる。

・ユースケースシナリオをVDMのテストデータとして表現する

・要求仕様を作成

・VDMに書き換え

・VDMで、テストデータを通す。

VDMのテストデータは、下流工程の実装用のテストデータとしても使える。

なので、だれかが要求仕様書からVDMを作成する方法を提示すればいい

そのアイデアはあるらしいが、具体的な実装にいたっていない。

ただ、これができると・・・仕様書もデモでき、アジャイルに載ってくる?・・・

ってなわけで、組み込み、大規模で採用できるだけの技術的な革新が起こる可能性がある。

コレが起こってしまうと、アジャイルが一気にこの分野に採用され・・・

・・・ウォーターフォールが敗退する可能性が、実はある。

結局、自分の耳障りのいい顧客の声しか聞かないから、顧客第一主義をとっても、事業は傾く

http://blog.goo.ne.jp/xmldtp/e/b248169c7f4afc4506343dbf83557c18

だけど、問題は、既存企業は、新興企業に負けて、撤退にまで追いやられるということ。

つまり、市場がなくなってしまうのだ。

アジャイルとウォーターフォールの関係もそうといえる。

昨日も掲示した、以下の図において

ウォーターフォールはA社、アジャイルはB社といえる。

アジャイルは、Web開発の場合は有効だけど、

・組み込みの場合、ハードは容易に変更できない

・大規模な場合、ドキュメントが必要になるが、要求仕様や論理的な設計の場合、

デモする術が無いので、イテレーション内に確認して、顧客と同意を取りながら、

開発することができない

(レビューはできるかもしれないが、それが可視化している、進捗わかるとはいえない)

等などの理由により、組み込み、大規模開発には、向かないとされている。

また、ウォーターフォールを採用しているSIerさんは、そういう顧客の意見を聞いているので、

市場の変化に気づかない。

しかし、上記2つは、大きく変わる可能性がある。

■ハードもアジャイル化できる可能性が出てきた

FPGAのエミュレーター(シミュレーターではない)Veloceにより、ハードを製作しなくても(する前に)ソフトウェア開発、テストができるようになった。

また、ハードのテストも、Questa inFactなどにより、制約つきランダムテストよりも高い網羅性と高速のテストが可能になった(人手よりも、当然早い)。

これらにより、ハード設計とソフト開発が同時並行的に進められ、修正スピードも劇的に(100倍以上とか)早くなった。

そうなってくると、・・・ハードもアジャイル?

■要求仕様や論理的な設計のデモも・・・実はできる!

だれもいわないけど、要求仕様や論理的な設計のデモって、実は、できる。

その前に、ライブラリのデモであれば、FDDを採用して、JUnitでテスト環境を作成しておき、

イテレーション内でプログラムを作成、JUnitで通ることを示せば、デモ?できる。

これとおなじレベルであれば、要求仕様のチェックはできる。

・ユースケースシナリオをVDMのテストデータとして表現する

・要求仕様を作成

・VDMに書き換え

・VDMで、テストデータを通す。

VDMのテストデータは、下流工程の実装用のテストデータとしても使える。

なので、だれかが要求仕様書からVDMを作成する方法を提示すればいい

そのアイデアはあるらしいが、具体的な実装にいたっていない。

ただ、これができると・・・仕様書もデモでき、アジャイルに載ってくる?・・・

ってなわけで、組み込み、大規模で採用できるだけの技術的な革新が起こる可能性がある。

コレが起こってしまうと、アジャイルが一気にこの分野に採用され・・・

・・・ウォーターフォールが敗退する可能性が、実はある。